LQT, les initiales de « La Question Technique », un nouveau rendez-vous hebdomadaire que nous lançons ce jour sur PCWorld.fr pour vous aider à mieux comprendre l’informatique. Et on commence très technique avec le B.A.BA : le transistor.

LQT, les initiales de « La Question Technique », un nouveau rendez-vous hebdomadaire que nous lançons ce jour sur PCWorld.fr pour vous aider à mieux comprendre l’informatique. Et on commence très technique avec le B.A.BA : le transistor.

Imaginé dès les années 1920 comme le successeur des tubes à vide (ou lampes à radio) et fabriqué pour la première fois en 1947 par trois chercheurs du Bell Labs aux États-Unis (récompensés par un Nobel de physique), le transistor est devenu en quelques décennies un composant absolument indispensable dans de très nombreux domaines, puisqu’il est au cœur de tous les appareils électroniques. Votre ordinateur et votre smartphone peuvent en contenir plusieurs centaines de milliards, votre TV des centaines de millions, et même votre réfrigérateur en contient sans doute plusieurs dizaines de milliers. Mais au fait, c’est quoi exactement un transistor, et à quoi ça sert ?

Un transis-quoi ?

Le transistor est un composant électronique à trois contacts (tri-pôle). Pour les transistors les plus utilisés en électronique numérique (transistors à effet de champ, FET), ces trois contacts sont baptisés « grille », « drain » et « source » (gate, drain et source en anglais).

Électriquement, le transistor peut être vu comme un interrupteur/variateur contrôlé par un signal électrique : la tension présente entre la grille et la source permet de contrôler la circulation du courant entre le drain et la source. Dès que cette tension dépasse une certaine valeur (la tension de seuil), le courant peut circuler entre la source et le drain. Selon le type de transistor, cette circulation peut se faire soit lorsque la tension est inférieure au seuil (transistor P), soit lorsqu’elle est supérieure (transistor N). Certains transistors sont donc en position ouverte au repos, tandis que d’autres sont bloqués.

Physiquement, un transistor peut être fabriqué selon plusieurs dizaines de procédés différents. Le plus courant est le MOSFET (Metal Oxide Semiconductor Field Effect Transistor). Un transistor MOSFET à canal N est réalisé sur un substrat de semiconducteur (généralement du silicium), faiblement appauvri en électrons (on parle de « dopage P »), et dans lequel sont injectés des ilots enrichis en électrons (« dopage N ») pour constituer la source et le drain. Un MOSFET à canal P est fabriqué sur le même principe, avec un dopage inversé. La zone située entre les deux ilots est ensuite oxydée, pour la rendre isolante, puis recouverte de métal ou de silicium fortement dopé pour constituer la grille.

Lorsqu’une tension est appliquée sur la grille (ce qui représente un 1 en binaire), elle induit un champ électrique qui renforce la conductivité d’un canal N, laissant alors passer le courant (1 binaire) dans un transistor N, ou diminue la conductivité d’un canal P, provoquant la fermeture (0 binaire) d’un transistor P. Lorsque la tension est relâchée, le transistor retrouve son état initial, fermé pour un N, ouvert pour un P.

D’accord, et ça sert à quoi au juste ?

Pour fonctionner, un circuit électronique numérique a besoin de composants capables d’effectuer les opérations logiques de l’algèbre de Boole. Il s’agit d’opérations mathématiques fonctionnant uniquement sur des valeurs binaires, avec une valeur de sortie qui dépend d’une ou plusieurs valeurs d’entrée.

Toutes les opérations de l’algèbre booléenne, quel que soit leur nombre de variables et leur complexité, peuvent se résumer en une combinaison de trois fonctions logiques de base (ou portes logiques quand on parle de leur implémentation dans un circuit électronique) : NON (la sortie vaut l’inverse de l’entrée), ET (opération à deux entrées dont la sortie vaut 1 si les deux entrées valent 1) et OU (opération à deux entrées dont la sortie vaut 1 si au moins une des entrées vaut 1).

Par exemple, la fonction NAND (NOT-AND), que l’on connait pour être à la base de la plupart des mémoires flash (il en existe aussi en NOR, plus performantes dans certains cas mais bien plus onéreuses) est la combinaison d’une fonction ET et d’une fonction NON.

En électronique, on utilise deux tensions de référence, une tension haute qui représente le 1, une tension basse (généralement mise à la masse) qui représente le 0. Effectuer des calculs binaires avec un circuit électronique nécessite donc de disposer de circuits capables d’accepter plusieurs signaux en entrée et de positionner le signal de sortie soit au niveau haut, soit au niveau bas, en fonction des niveaux des signaux d’entrée et de l’opération logique qui doit être effectuée.

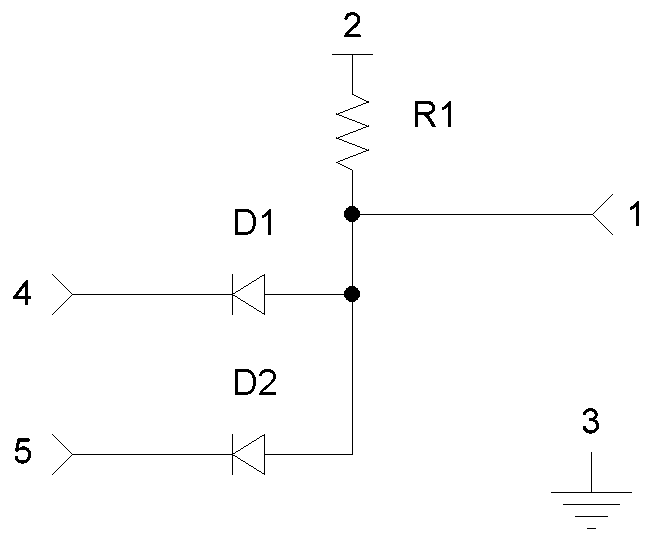

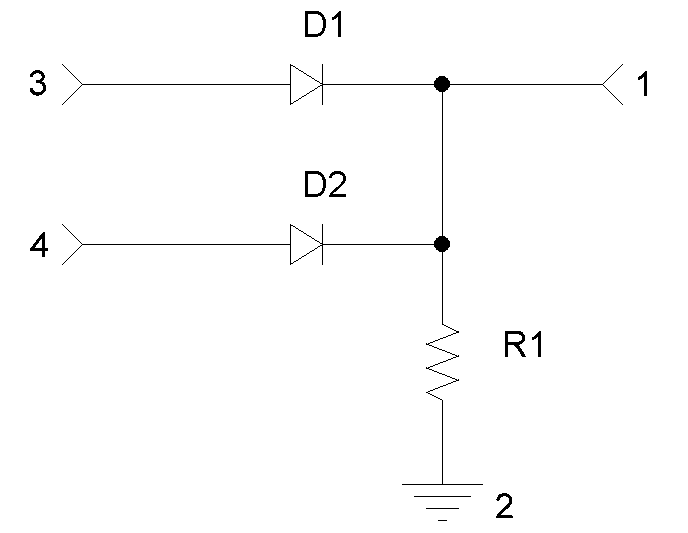

Et c’est là qu’intervient ce bon vieux transistor, nécessaire à la fabrication des portes logiques. En effet, s’il est possible de réaliser des portes ET et OU avec une simple combinaison de diodes et de résistances, aucun dipôle ne permet de réaliser une porte NON.

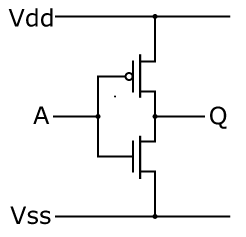

L’opération devient par contre possible avec des transistors, en utilisant une tension haute supérieure à la tension de seuil du transistor. Par exemple en combinant un transistor P et un transistor N selon le schéma suivant :

Si A vaut 1 (Vss) le transistor P se bloque et le N s’ouvre, raccordant Q au niveau bas (Vdd). La sortie vaut donc 0. Si A vaut 0 (Vdd), c’est le transistor N qui se bloque et le P qui s’ouvre, raccordant Q au niveau haut (Vss). La sortie vaut donc 1.

Si A vaut 1 (Vss) le transistor P se bloque et le N s’ouvre, raccordant Q au niveau bas (Vdd). La sortie vaut donc 0. Si A vaut 0 (Vdd), c’est le transistor N qui se bloque et le P qui s’ouvre, raccordant Q au niveau haut (Vss). La sortie vaut donc 1.

Notez qu’en fait un seul transistor P (respectivement N) serait suffisant sur le plan logique, en raccordant Q au niveau bas (respectivement, au niveau haut) à travers une résistance.

Ce montage basé sur deux transistors au fonctionnement opposé est le principe de base de la technologie CMOS (Complementary MOS), qui consiste a systématiquement utiliser les transistors par paires complémentaires (P et N), assemblés de tel que l’un soit bloqué lorsque l’autre est ouvert.

Ce type de montage n’est bien entendu pas là pour gonfler le nombre de transistors sur les fiches techniques (il en nécessite deux fois plus), mais pour réduire la consommation électriques des circuits électroniques. En effet, avec un seul transistor la résistance qui raccorde la sortie à l’un des deux lignes de référence engendre une dissipation thermique non négligeable lorsqu’elle est traversée par un courant, c’est-à-dire dès que la sortie n’est pas à la même tension que la ligne à laquelle elle a été raccordée.

En pratiques, les portes ET et OU sont généralement réalisées elles aussi avec des transistors pour réduire la consommation électrique en éliminant les résistances.

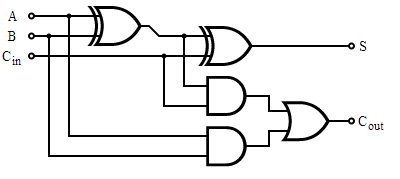

Il ne reste ensuite plus qu’à connecter entre elles de quelques milliers à quelques dizaines de milliards de portes pour réaliser des puces capables d’opérations toujours plus complexes. Une addition binaire sur n bits peut par exemple être réalisée avec une cascade de n blocs constitués de deux portes XOR (OU exclusif, vaut 1 si une seule des deux entrées vaut 1), deux portes ET et une porte OU assemblées suivant le schéma suivant :

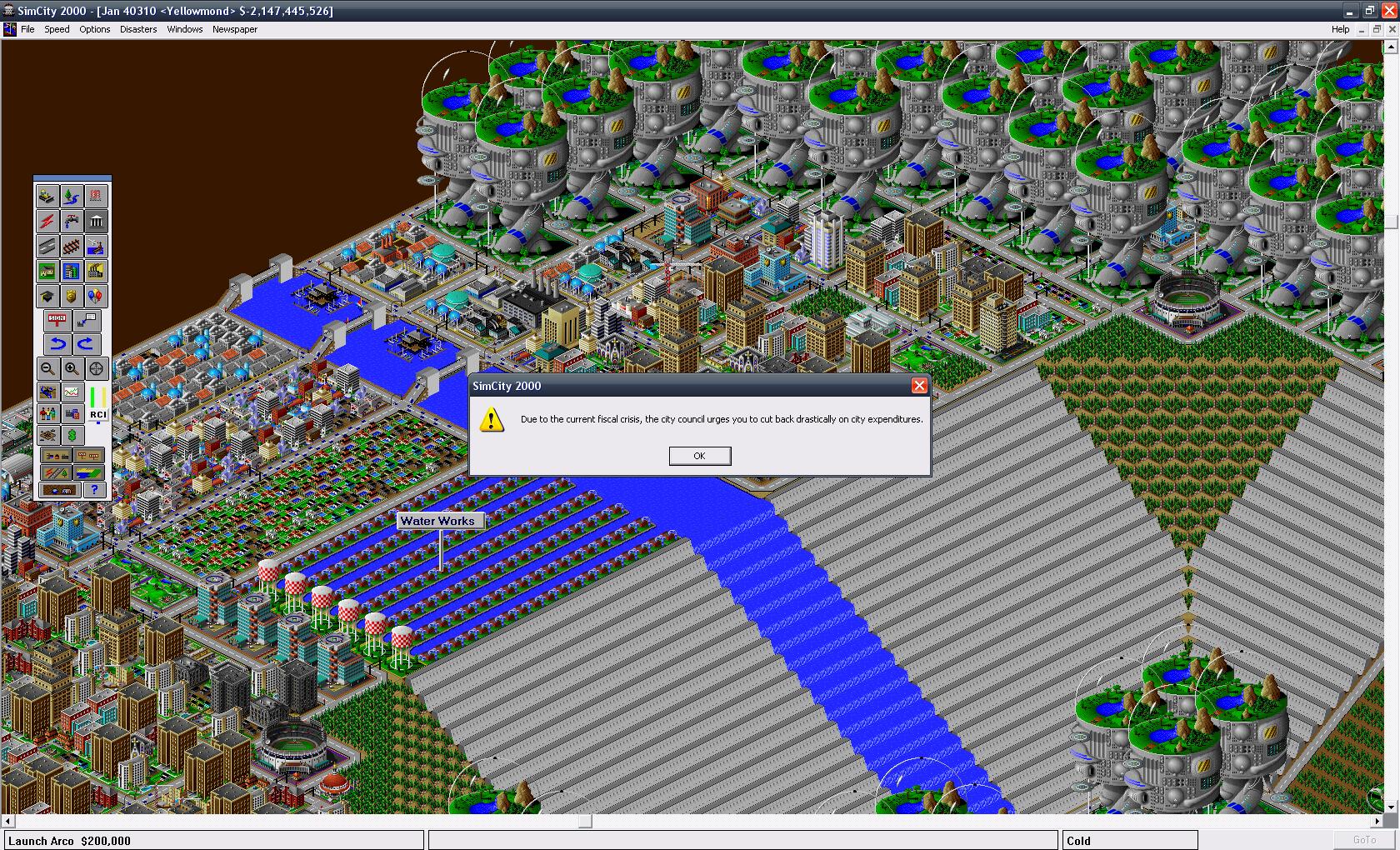

En entrée, pour le bloc de rang i, A et B sont les bits de rang i des nombres à additionner, Cin la retenue du rang (i – 1). En sortie, S sera le bit de rang i du résultat de l’addition et Cout la retenue à propager au range supérieur. Si la retenue vaut 1 au dernier rang, l’addition échoue : le résultat ne peut plus être représenté sur n bits, il y a « overflow ». Pour l’anecdote, c’est l’overflow qui peut parfois provoquer le passage à un score négatif dans un jeu, lorsque le score est géré avec des entiers signés (c’est-à-dire pouvant être positifs ou négatifs) : le calcul d’un nouveau score « déborde » et va modifier le bit qui indique normalement le signe du nombre. Il passe de 0 (positif) à 1 (négatif), et c’est le drame, vous passez soudainement de 2 milliards de simflouze à -2 milliards… Ce qui n’est pas exactement la même chose, les maires amateurs dans SimCity pourront en témoigner !

En entrée, pour le bloc de rang i, A et B sont les bits de rang i des nombres à additionner, Cin la retenue du rang (i – 1). En sortie, S sera le bit de rang i du résultat de l’addition et Cout la retenue à propager au range supérieur. Si la retenue vaut 1 au dernier rang, l’addition échoue : le résultat ne peut plus être représenté sur n bits, il y a « overflow ». Pour l’anecdote, c’est l’overflow qui peut parfois provoquer le passage à un score négatif dans un jeu, lorsque le score est géré avec des entiers signés (c’est-à-dire pouvant être positifs ou négatifs) : le calcul d’un nouveau score « déborde » et va modifier le bit qui indique normalement le signe du nombre. Il passe de 0 (positif) à 1 (négatif), et c’est le drame, vous passez soudainement de 2 milliards de simflouze à -2 milliards… Ce qui n’est pas exactement la même chose, les maires amateurs dans SimCity pourront en témoigner !

En non signé, le score repartira simplement de zéro, tandis que si le jeu est prévu pour détecter l’overflow, il se contentera probablement de figer le score à la valeur maximale possible.

Ton transistor, il est puissant, mais il a bien des limites ?

Même si la communication des fabricants de puces au sujet des transistors qui constituent leurs produits se limite souvent à indiquer leur nombre et leur finesse, certaines caractéristiques bien connues de nos puces sont en fait étroitement liées aux caractéristiques, et surtout aux limites de ces transistors.

C’est en particulier le cas de la fréquence. Lorsqu’un transistor passe de l’état ouvert à l’état fermé, il faut en effet un petit délai avant que la tension entre la source et le drain se stabilise. Il faut donc que le composant qui lit la sortie de ce transistor attende un instant avant de la lire. C’est ce délai qui limite la fréquence maximale de fonctionnement de la puce : même si la puce est correctement refroidie, elle ne pourra plus effectuer ses opérations logiques correctement si le temps de réponse de ses transistors est supérieur à la durée d’un cycle d’horloge (inverse de la fréquence).

Les problèmes de température que l’on peut parfois rencontrer sont souvent eux aussi liés au fonctionnement des transistors. En effet, la tension de seuil des transistors varie avec la température. Plus la température augmente, plus la tension de seuil augmente. Si la température devient trop élevée, un transistor peut donc se « figer » parce que la tension du niveau haut devient trop faible par rapport à la tension de seuil… Un problème d’autant plus problématique que la température augmente avec la tension d’alimentation…

À l’inverse, le « cold bug », bien connu des overclockers de l’extrême, qui limite parfois la montée en fréquence de processeurs trop bien refroidis, peut notamment provenir de l’augmentation du temps de réponse des transistors à basse température, qui limite du coup la fréquence maximale atteignable.

Enfin, la limite la plus problématique aujourd’hui provient des courants de fuite. Plus un transistor est gravé finement, plus il devient difficile de contenir les courants parasites qui le parcourent, les couches isolantes perdant leur efficacité en s’affinant. Ces courants de fuite ont pour l’instant relativement peu d’impact sur le plan logique, mais posent par contre déjà des problèmes de consommation électrique, et donc de chauffe des puces. Et en augmentant encore la finesse de gravure, ces courants de fuite finiront par devenir trop élevés, empêchant complètement le fonctionnement du transistor.

Mais du coup, on va quand même continuer à les utiliser à l’avenir ?

Malgré leurs limites, les transistors sont sans doute encore là pour longtemps, et même pour très longtemps. Ils ont en effet atteint une telle importance que leur remplacement n’est quasiment pas envisageable pour l’instant sans revoir totalement la logique de fonctionnement des appareils électroniques. Outre l’affinement de la gravure, les recherches d’aujourd’hui s’orientent donc principalement sur des solutions pour repousser toujours plus loin les limites des transistors, plutôt que pour les remplacer par d’autres types de composants.

L’une des pistes actuellement étudiée est l’utilisation d’un substrat de graphène à la place du silicium. Le graphène est une fine feuille de carbone, faisant seulement un atome d’épaisseur. Mais celui-ci ne dispose pas de propriétés semi-conductrices en conditions normales, ce qui devrait mener à des transistors au fonctionnement très différent de celui des transistors actuels, obligeant à revoir les schémas fonctionnels des principaux blocs logiques. Une révision qui pourra d’ailleurs parfois être bénéfique sur le plan de la complexité. Par exemple, une porte XOR pourrait par exemple être réalisée avec seulement trois transistors au graphène, contre huit transistors au silicium.

Mais la plus grosse révolution viendra probablement des transistors optiques, qui reproduisent le comportement des transistors classiques, mais en remplaçant les signaux électriques par des signaux optiques, avec à la clé une amélioration des temps de réponse et une réduction de la consommation d’énergie. La miniaturisation pourrait également être poussée encore plus loin. En Allemagne, l’institut Max Planck a par exemple réussi à réaliser un transistor optique composé d’un seul atome déposé dans une petite cavité transparente.

Article bâclé, trop rapide, il sert à quoi ?

L’anecdote arrive comme un cheveu sur la soupe. Sans connaître un minimum d’électronique numérique (sans parler d’algèbre de Boole), personne ne comprendra. Et ce qui peuvent comprendre connaissent déjà.

Il aurait été plus judicieux de parler de la porte NAND et de pourquoi c’est la porte de base utilisée partout : la porte AND est en réalité une NAND suivie d’une NOT et non le contraire pour des raisons de nombre de transistors.

Sans compter qu’il manque un minimum de références pour que les lecteurs qui suivent jusqu’au bout sachent où aller ensuite.

Au niveau de l’implémentation électronique, oui. Au niveau logique, non, la fonction logique NAND est bien définie comme étant un AND suivi d’un NOT. Les trois opérations de base sont le AND, le OR et le NOT, les autres sont une définies à partir de ces trois là, même s’il est vrai que le NAND à lui seul est complet et peut permettre de redéfinir toutes les autres, y compris le AND (deux NAND en série avec la sortie du premier sur les deux entrées du second) et le OR (deux NAND prenant chacun deux fois une des deux entrées, et un troisième qui prend en entrée les sorties des deux premiers).

L’anecdote, c’était juste pour illustrer ce que peut provoquer un overflow au niveau logiciel, histoire d’avoir quelque chose d’un peu concret.

Et bien sûr que ceux qui connaissent l’électronique numérique n’apprendront rien avec cet article. Reste à voir si ceux qui ne connaissent pas comprendront, et là je serais pas forcément aussi catégorique que toi…

Au niveau logique aussi, tu peux les définir comme tu veux. Le souci, c’est ta phrase :

Elle laisse à supposer que l’implémentation est faire par une AND suivie d’une NOT.

Encore une fois faux. Tu as juste besoin de AND et NOT ou de OR et NOT. Je chipotte, d’accord (tu dis toi-même que la NAND suffit, et c’est normal puisqu’on utilise quasiment qu’elle partout).

Pour que l’anecdote soit vraiment parlante, il manque des choses au milieu. Normal que tu veuilles illustrer, mais c’est un peu comme parler des bases de la programmation et parler en même temps d’un truc super pointu fait 5 ou 6 niveaux de détail au-dessus.

Je ne dis pas non plus que j’aurai fait mieux (sans doute pas).

Mais le fait est qu’au niveau logique, le NAND est bien défini comme la combinaison d’un AND et d’un NOT, définition qu’on retrouve jusque dans son nom…

C’est vrai que la phrase est pas forcément claire, mais à ce stade là de l’article je parlais encore de l’aspect logique, pas de l’implémentation CMOS, que j’aborde plus loin.

D’autant plus que la façon de faire les portes dépend beaucoup de l’implémentation. En CMOS, c’est vrai qu’on utilise généralement le NAND et le NOT comme unités de base, mais en RTL par exemple il me semble qu’on fait des AND directement (et les NAND également, les deux ayant la même complexité).

Pas d’accord. Même si NAND tout seul suffit, ou encore NOR tout seul, ou encore AND + NOT et OR + NOT, le fait est qu’en logique quand on découpe des opérations, on découpe en utilisant AND, OR et NOT comme opérations de bases, probablement parce que ce sont les plus simples à comprendre et que c’est plus simple d’utiliser ces trois opérations que de tout ramener à une seule, pour pas se retrouver avec des formules de 3 km… va par exemple regarder la formule du XOR en AND/OR/NOT et celle en NAND, y’en a une qu’à peu près n’importe qui peut comprendre au premier coup d’œil, l’autre nom.

Ben la ça me parait faux, on a ni la même rapidité ni le même cout en surface, une NAND coute 4mos et 1 propagation, une AND coute 6mos et 2 propagations (NON NAND). Ça m’étonnerait que tu puisses négliger ça lors de ton implémentation physique.

sinon pour le Vt inversement proportionnel a la température, personne pour confirmer?

Euh, t’es sûr de ça ? Pour moi en RTL un NAND c’est 2 transistors et 3 résistantes, et un AND idem.

J’ai clairement en tête un cours de semicond où le prof nous avait expliqué qu’il fallait augmenter la tension pour compenser l’augmentation de la tension de seuil avec l’échauffement, mais ma mémoire me joue peut-être des tours, je vais essayer de retrouver ce cours.

EDIT : en attendant, j’ai trouvé ça qui semble confirmer une augmentation de la tension de seuil avec la température, mais c’est du Wiki, donc je sais pas ce que ça vaut niveau fiabilité : https://fr.wikiversity.org/wiki/Transistor/Transistor_MOSFET

Et ça qui parle d’une baisse de 2mV par °C, mais pour des transistors bipolaires, pas pour des FET : http://cignus2.free.fr/cours/transistors/bipolaire.htm

@SartMatt> merci de répondre :jap:

Je ne sais pas l’abstraction au niveau RTL (frontend), peut être que l’optimisation est faite dans un second temps, au niveau backend.

En tout cas en « standard cell », la brique de base pour le digital, le NAND et le NOR sont les plus simples a faire (apres l’inverseur), pour N entrées on a N mos en série et N mos en //, soit 2*N mos. Ensuite on a les AND et OR, puis les XOR et les cells les plus complexes sont les latchs.

Je fais du layout analogique, on a tjrs un peu de digital a intégrer…

Pour le Vt ca n’est pas linéaire et selon les technos il y a d’autres effets de bords qui peuvent finir par annuler cet effet dans certains corners, mais je m’en couperai bien une sur la tendance globale, je t’invite a vérifier stp

http://ieeexplore.ieee.org/%5B…]3Farnumber%3D1476529

[edit aussi] ben oui j’ai la même formule en gros sur le wiki en :strange: pourtant a la ligne d’après ils parlent de -2mV/°

http://en.wikipedia.org/wiki/Threshold_voltage

Bon je vais chercher un peu plus….

Je ne suis pas d’accord avec toi. L’algèbre de Boole, c’est niveau 1ère S si je ne m’abuse (à moins que je n’en aie fait en terminale), donc c’est du niveau lycée.

En ce qui concerne l’électronique, on aborde les composants électriques en classe de 4è (parfois 5è). On est ici sur du niveau collège.

Donc, oui, on peut très bien comprendre cet article — que j’ai, au passage, beaucoup apprécié — sans pour autant être un crack en électronique, ni en mathématiques.

Excellent article, bienvenue nouveau rédacteur?

Juste 2 points:

1/ Il faut donc que le composant qui lit la sortie de CE transistor (faute a corriger SVP)

2/ L’accroissement de température rend tous les passifs moins performants, mais c’est le contraire au niveau silicium : Le bruit généré par la chaleur rend les électrons plus mobiles et plus éloignés du noyaux, ils ont tendance a sauter plus facilement. Ce qui réduit le Vt du transistor, il y a besoin de moins de champ pour faire passer l’électron.

C’est ce phénomène qui peut provoquer un emballement thermique en analogique : ça chauffe, donc ça baisse le Vt, donc plus de courant passe, donc ça chauffe plus, et on reboucle…

:chinois: merci

Corrigé :jap:

Article sympa, mais…

« Votre ordinateur et votre smartphone peuvent en contenir plusieurs centaines de milliards »

…ici l’auteur s’emballe un peu. 🙂

Edit : quoique, avec un paquet de mémoire Flash, ça le fait.

Yep, c’est à ça que je pensais 😉

En flash MLC 2BPC, rien que pour le stockage, sans compter tous les transistors pour gérer l’adressage, on est à 4 milliards de transistors par Go, donc dès qu’il y a plus de 25 Go de flash, on dépasse les 100 milliards des transistors…

Et sur les PC, y a aussi la RAM, avec 1 transistor par bit il suffit d’un peu plus de 12 Go pour avoir 100 milliards de transistors.

Rien qu’avec RAM et flash, j’arrive à 2 176 milliards dans mon PC. Le CPU et le GPU deviennent négligeables du coup 😀

Matthieu Sarter == SartMatt, putain j’avais même pas percuté ! 😀

Sinon oui c’est vrai que quand on pense « milliards de transistors » on pense d’abord aux CPU et surtout aux GPU, mais finalement la RAM et a fortiori la Flash en consomment bien plus.

@Mathieu Chartier> merci

Pour l’effet de la température, je n’ai pas trouvé de lien simple; Il y a 2 phénomènes conjugués quand la temp augmente:

Le courant max baisse du a la résistance augmentée du canal.

Le leakage augmente et le seuil de déclenchement Vt (threshold) baissent,pour le Vt de 2 a 4mv/°C (http://en.wikipedia.org/wiki/Threshold_voltage)

Donc en prenant Vt=500mV a 20°C

a -180°C on aurait un Vt=900 a 1300mV

a 80°C on a un Vt=260 a 380mV

Le cold bug pourrait venir de cette augmentation de Vt dans une architecture particulière.

Et donc une phrase de l’article me parait erronée:

» Plus la température augmente, plus la tension de seuil augmente. «

Moi en tout cas, je trouve l’article bien fait car il présente les bases sans trop rentrer dans les détails.

Pour la température en effet, le seuil diminue. Pour comprendre cela, il faut comprendre qu’à la base, le semiconducteur fonctionne en apportant une énergie qui permet aux charges de traverser ce que l’on appelle une bande interdite (« Band Gap »)

La taille de cette bande a généralement tendance à diminuer avec la température.

Quand on parle de semi-conducteurs, il faut toujours penser à VT = k*T/q (k = constante de Boltzmann ; T la température ; q la charge élémentaire) qui est le « thermal voltage » (à ne pas confondre avec Vth, la tension de seuil)

Ce rapport se retrouve dans pas mal d’équations (pas besoin de détailler) mais on a notamment pour les MOS :

-Plus de fuite à haute température

-Moins de courant à haute température (le rapport entre courant de drain et tension GS)

-Seuil moins élevé.

Pour résumer, il faut souvent moins de tension pour commencer à faire conduire le MOS, mais plus de tension pour avoir un courant donné.

Un peu dense comme article : Chaque paragraphe est +/- 1h de cours d’électronique, et à lire 3x 🙂

L’intension est louable, c’est quand même un sujet un peu barbu pour le néophyte !

Bref, mission accomplie ! Evidemment, les (vrais) spécialistes n’apprennent pas grand chose des articles de vulgarisation ou d’initiation dans leur domaine. Les autres y trouvent des bases, des rappels ou un début de lexique, au moins pour comprendre l’esprit de ce qui s’y passe. La critique reste bien plus facile que l’art.

Vous avez des rapports avec CPC ? pas la première fois que je constate des similitudes de sujets entre PCWorld et CPC à quelques semaines/jours de distance… Enfin ici le dossier de CPC est vraiment bien foutu même si comme d’hab avec l’électronique je n’y est pas compris grand chose 😀