Cette semaine, La Question Technique s’intéresse à la fabrication des processeurs. Piqûre de rappel pour certains ou découverte pour d’autres, un article qui nous redonne l’occasion de poser les bases du travail des fabricants de l’industrie du semi-conducteur.

Avant d’arriver sur votre carte mère, votre processeur a subi de nombreuses opérations, transformant un matériau des plus banals en un petit bijou de technologie. Mais connaissez-vous les principales étapes de cette fabrication ?

Des grains de sable au wafer…

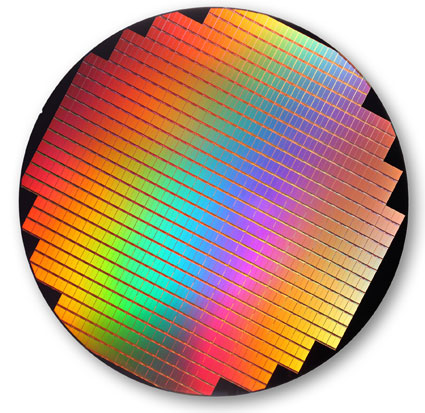

La première grande étape, qui n’est généralement pas effectuée par les fondeurs eux-mêmes, est la production des wafers, ces grandes galettes de silicium qui servent de base à la production de toutes les puces électroniques.

Le silicium en lui-même est un matériau peu onéreux, car très abondant sur terre : sa forme la plus courante, la silice, ou dioxyde de silicium (SiO2), représente environ 60% de la masse de la croûte terrestre et est le constituant principal du sable.

Mais dans l’électronique, il faut du silicium particulièrement pur, de 99,9% pour la production de panneaux solaires à 99,9999999% pour la production de processeurs (moins d’un atome « étranger » par milliard d’atomes de silicium). Cette purification est généralement réalisée en deux étapes.

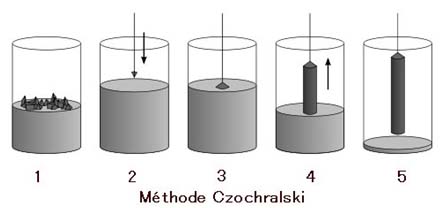

Tout d’abord, un lingot cylindrique de silicium monocristallin est fabriqué via le procédé de Czochralski : une « graine » de silicium monocristallin est plongée dans un bain de silicium liquide puis est lentement tirée vers le haut tout en tournant autour d’un axe vertical. Le silicium liquide va alors progressivement se solidifier autour de la graine, en adoptant la même structure cristalline. On obtient alors un lingot cylindrique de silicium très pur, pouvant atteindre plus d’un mètre de long et d’un diamètre généralement compris entre 25 et 450 mm, le plus courant pour les processeurs étant actuellement le 300 mm.

Tout d’abord, un lingot cylindrique de silicium monocristallin est fabriqué via le procédé de Czochralski : une « graine » de silicium monocristallin est plongée dans un bain de silicium liquide puis est lentement tirée vers le haut tout en tournant autour d’un axe vertical. Le silicium liquide va alors progressivement se solidifier autour de la graine, en adoptant la même structure cristalline. On obtient alors un lingot cylindrique de silicium très pur, pouvant atteindre plus d’un mètre de long et d’un diamètre généralement compris entre 25 et 450 mm, le plus courant pour les processeurs étant actuellement le 300 mm.

Ce lingot est ensuite purifié par la technique de la zone fondue. Lorsque le cristal est fondu puis se recristallise progressivement, les impuretés ont tendance à se concentrer soit dans la partie encore fondue, soit dans la partie recristallisée. La méthode de la zone fondue consiste à faire fondre une tranche du lingot à partir d’une extrémité, puis à déplacer lentement cette zone vers l’autre extrémité, ce qui permet de déplacer progressivement les impuretés. Cette opération doit généralement être répétée plusieurs fois pour atteindre un degré de pureté suffisant.

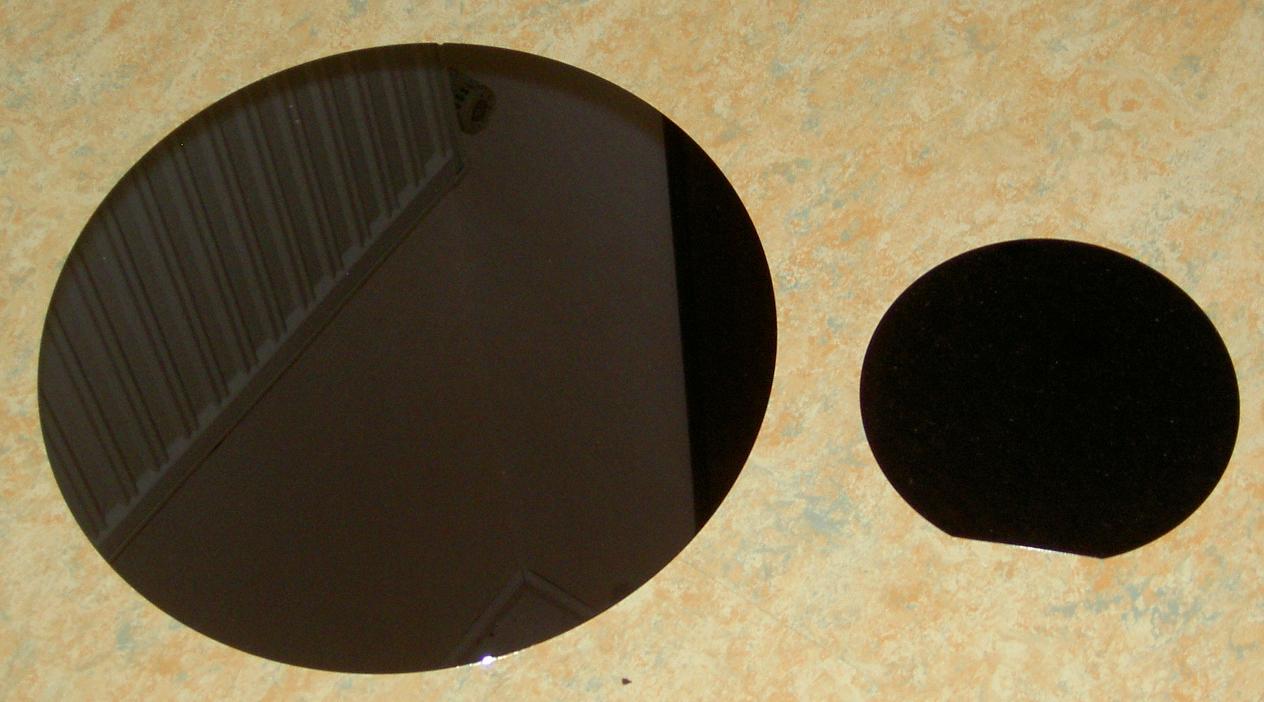

Une fois que le lingot a atteint une pureté suffisante, il est débité en fines tranches (moins d’1 mm d’épaisseur), qui sont ensuite polies pour en éliminer la moindre aspérité. Pour améliorer encore la pureté de la couche supérieure du wafer, une fine couche de silicium y est parfois déposée après la découpe, par épitaxie en le trempant dans un bain de vapeur de silicium.

Du wafer au die

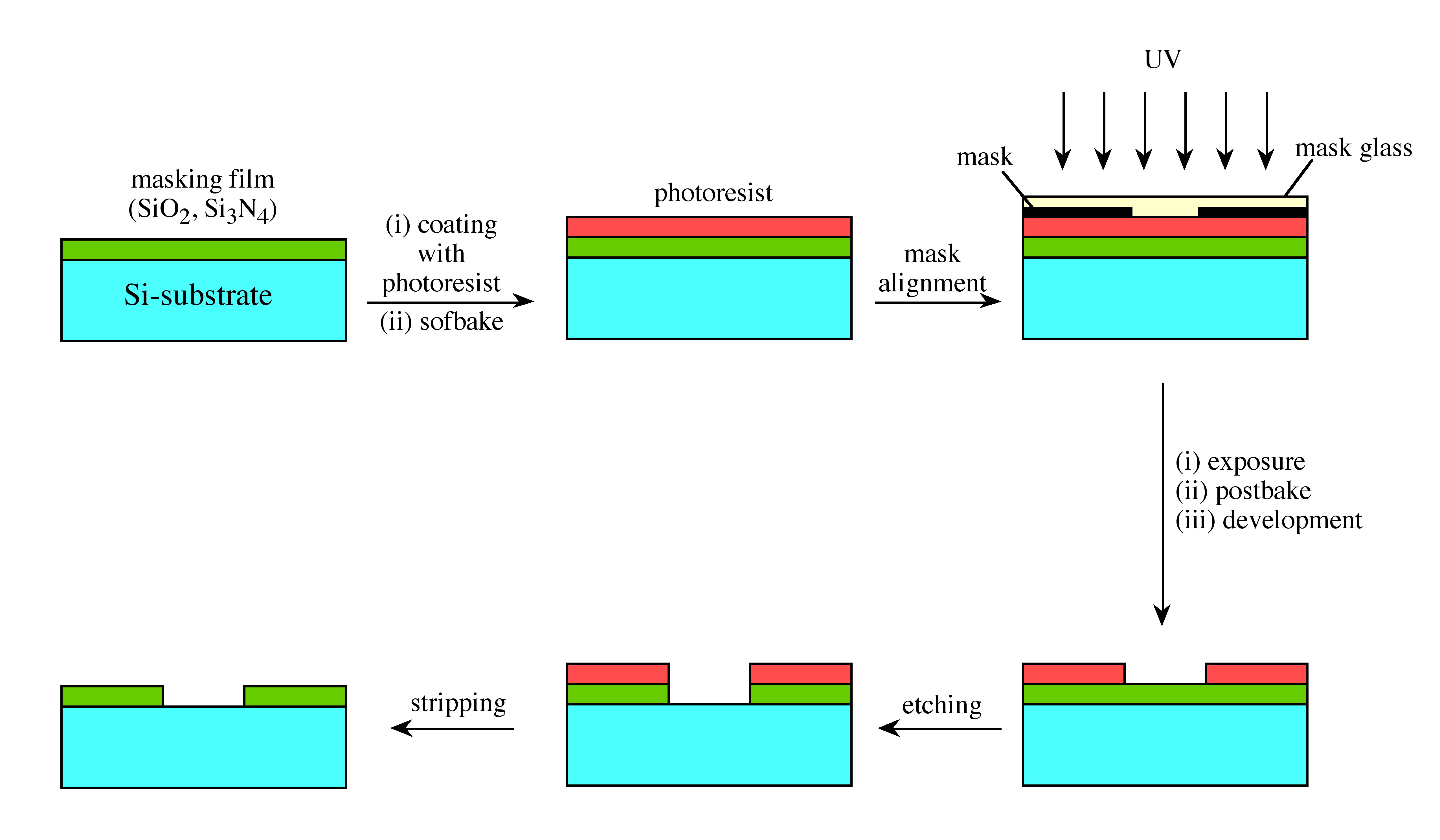

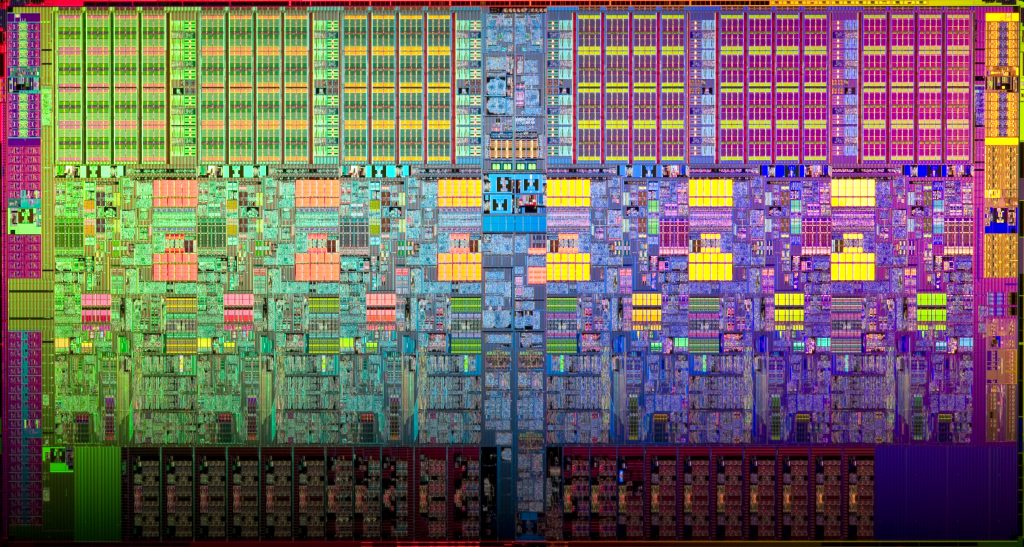

Une fois le wafer obtenu, il est chauffé dans une atmosphère riche en oxygène, ce qui permet d’obtenir une couche d’oxyde de silicium (oxydant) sur la surface. Le fondeur peut alors passer à la réalisation des die, par photolithographie.

Pour ce faire, le wafer est couvert d’un vernis sensible à la lumière UV. Le wafer passe ensuite sous un projecteur UV qui va projeter dessus un masque, correspondant au schéma des circuits de la première couche du processeur. Le masque ne comporte en général le schéma que pour un seul die, et l’opération est donc répétée autant de fois que nécessaire pour couvrir toute la surface du wafer. Le wafer passe ensuite sous un solvant, qui va détruire les zones du vernis qui ont été soumises à la lumière UV, exposant ainsi la couche d’oxyde de silicium.

Un flux de plasma est ensuite projeté sur le wafer, ce qui va permettre d’arracher l’oxyde de silicium, sauf dans les zones où il est encore couvert par le vernis, laissant ainsi apparaitre le silicium pur. Le wafer est alors soumis à un faisceau d’ions, qui va permettre de doper le silicium dans les zones où il est apparent, pour réaliser les drains et les sources des transistors. Le reste du vernis est ensuite éliminé et une nouvelle couche isolante est déposée sur le wafer.

Le processus UV/plasma est alors à nouveau répété pour tracer les grilles des transistors, avant de déposer encore une fois une couche isolante sur toute la surface.

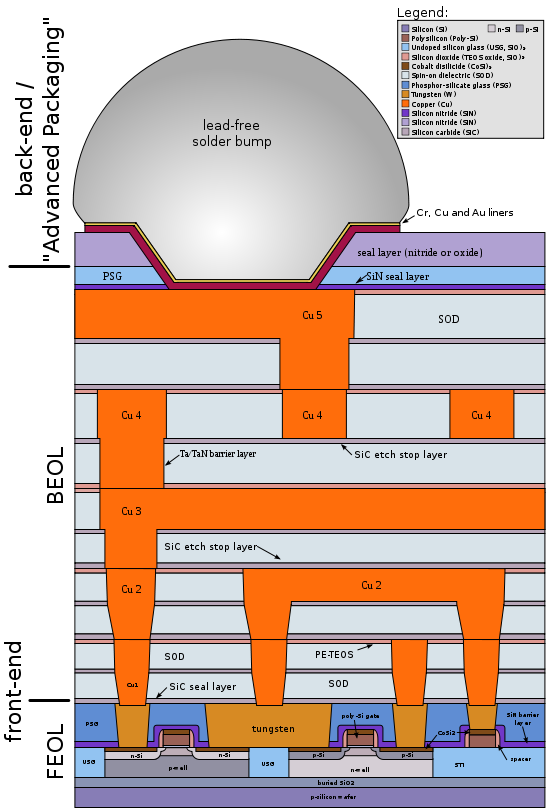

À ce stade, les transistors sont formés, et il reste donc à les interconnecter.

Une nouvelle étape de traitement UV/plasma va permettre de creuser des trous dans la couche isolante pour rejoindre les trois pôles de chaque transistor. Le wafer passe alors dans un bain de sulfate de cuivre pour déposer le cuivre sur le wafer par électrolyse, créant ainsi les contacts.

Le projecteur UV reprend du service pour tracer une première couche de circuit sur cette couche de cuivre. Le processus est ensuite répété une petite dizaine de fois, pour réaliser autant de couche de circuits que nécessaire, avec à chaque fois une couche isolante pour séparer les couches de circuits, percée de trous assurant les interconnexions entre les différentes couches.

Une fois toutes les couches réalisées un contrôle optique est effectué sur le wafer et chacun des dies subit divers tests de fonctionnement. C’est à ce moment qu’on mesure le rendement du wafer, c’est-à-dire le taux de puces commercialisables sur le wafer, également appelé « yields » par les industriels. Ce rendement détermine le coût de revient des puces. Le wafer est ensuite découpé et seuls les dies fonctionnels sont conservés.

L’obtention de rendements élevés nécessite une parfaite maitrise de la photolithographie, et ce d’autant plus que la gravure des processeurs est fine, ce qui explique que seule une poignée de fondeurs se partagent le marché. L’amélioration du processus de photolithographie est donc un axe clé pour les fondeurs et leurs fournisseurs d’équipements de lithographie (qui sont encore moins nombreux que les fondeurs…), qui développent main dans la main des processus toujours plus avancés et complexes, comme la photolithographie par immersion, qui consiste à ajouter une fine couche de liquide entre le wafer et le projecteur. La réfraction de la lumière par cette couche de liquide permet de réduire la taille du die sans réduire la taille du masque, ce qui permet de garder une plus grande précision.

Malgré tous ces efforts, il y a toujours des imperfections lors des différentes étapes de réalisation des puces, générant alors des dies non fonctionnels, les fabricants de processeurs prévoient généralement un peu de redondance dans les circuits principaux du CPU, pour permettre de contourner certains défauts. D’autres défauts sont contournés par la segmentation de la gamme. Par exemple, en proposant diverses capacités de cache, un die touché par un défaut au niveau de son cache pourra être utilisé pour une puce d’entrée de gamme.

Il y a aussi des dies non fonctionnels sur le pourtour du wafer, certains die « débordant » de celui-ci (parfois, le processus de production prend ce paramètre en compte dès la gravure, et ces dies ne sont donc pas gravés, mais la surface reste inévitablement perdue). C’est pour réduire ces chutes que le diamètre des wafers a progressivement augmenté : le nombre de dies chevauchant le bord du wafer est proportionnel au diamètre du wafer, alors que le nombre total de dies par wafer est proportionnel au carré du diamètre, donc plus le diamètre augmente, plus le taux de dies coupés diminue. Le gros de la production de processeurs se fait aujourd’hui avec des wafers de 300 mm, mais les fondeurs se préparent activement à la généralisation des wafers de 450 mm.

Du die au processeur

Une fois les dies découpés, le plus gros du travail est fait, il ne reste plus qu’un peu de « cosmétique » : placer le die dans un package qui permettra de manipuler facilement le processeur pour l’intégrer à une machine.

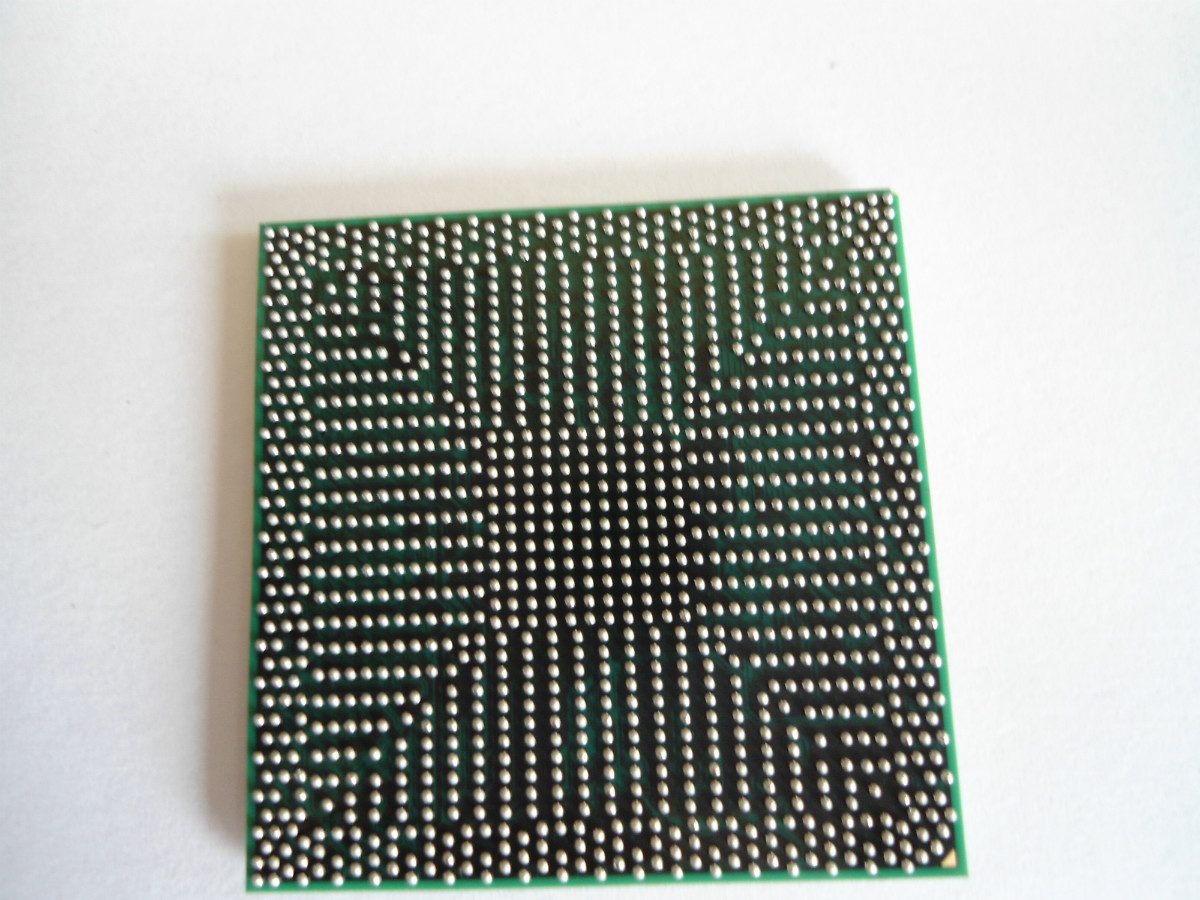

Le die est couvert de petites billes métalliques, connectées aux circuits du die et correspondant chacune à une des interfaces du processeur avec le monde extérieur.

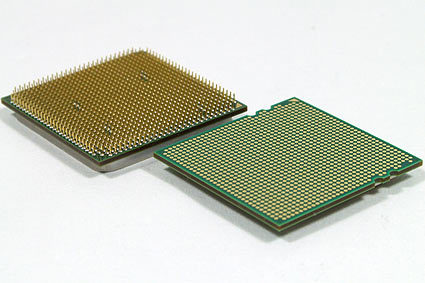

Ces billes étant petites et fragiles, le die va être installé sur un support plus grand, permettant d’espacer les contacts et de proposer des contacts plus solides et plus adaptés à l’utilisation qui sera faite du CPU. On retrouve différents types de supports, selon les modèles de processeurs.

Les processeurs destinés au machine de bureau utilisent généralement des packages qui fonctionnent par simple contact. Intel utilise par exemple le système LGA, où le package du CPU est couvert de contacts plats et se monte sur un socket composé de petites griffes métalliques qui font faire pression sur les contacts du CPU, tandis qu’AMD utilise le système PGA, où le package du CPU possède des centaines de pattes qui viennent s’enficher dans les trous du socket. Un système abandonné par Intel depuis quelques années, notamment pour faciliter la manipulation des puces et en finir avec les fameux pins tordus (dont les pinces à épiler de nos femmes se souviennent encore… chacun sa technique).

Du côté des processeurs mobiles, c’est le plus souvent le BGA qui est utilisé. Comme le die, le package est couvert de petites billes métalliques (qui sont toutefois plus grosses que sur le die), ce qui permet de le souder directement à la carte mère. Cette solution permet de gagner en épaisseur par rapport aux sockets LGA ou PGA, dont le mécanisme de rétention est relativement encombrant.

De l’autre côté du packaging, sur la face opposée à la carte mère, le processeur est souvent surmonté d’un capot métallique, le heatspreader. Comme son nom ne l’indique pas, il sert surtout à protéger le die, qui risquerait sinon d’être endommagé lors du montage du système de refroidissement. De façon plus marginale, il facilite le refroidissement, en le rendant moins dépendant de la qualité de l’interface entre le radiateur et le processeur (la surface de contact étant augmentée, l’interface peut être moins performante).

Une fois le processeur packagé, il subit une dernière batterie de tests, notamment pour déterminer la fréquence de fonctionnement et la tension qu’il faudra lui appliquer, puis il est marqué et emballé, prêt à être vendu.

Ces LQT hebdomadaires sont excellentes!

@loulnux> Oui, tout à fait. C’est un plaisir de revenir visiter pcworld le WE.

D’accord également, ce LQT est unique en son genre et toujours très intéressant 😀

Yes, member of the club, même si, parfois, le rappel de certaines données techniques et matérielles nous renvoient loin loin de nos petites machines si précises et pointues : ces gravures multicouches qui approchent la taille atomique (encore un effort tout de même !) sont vertigineuses. La conception de plus en plus statistique, presque probabiliste des circuits a de quoi faire réfléchir.

Toujours un régal de dévorer tout ces LQT 😉

Excellente idée ces Dossiers techniques cela permet de réviser ces connaissances

Vous voyez que ça sert à quelque chose de faire des « news » le week end… on en redemande !

Toujours très intéressante cette LQT,

Merci beaucoup pour cette dose de culture informatique

Excellent, très instructif, vive la LQT.

Ce fut un régal.

En effet, excellente vulgarisation !

Je pense qu’il faudrait prévoir un mot clé LQT, et/ou classer ces LQT dans la section DOSSIERS. Là elles sont publiées comme news perdu entre deux news sur un hypothétique iPhone 8, ou un projet QuickStarter +/- intéressante.

Je pense que ces articles ne sont pas dépendant du temps, et mériterait leur place en dehors de la timeline de news.

@fofo_4012> Absolument, je me suis fait la même reflexion. On peut toujours faire une recherche « LQT », mais une présence dans l’onglet « dossier » leur rendrait plus justice.

Merci à tous pour vos retours, ça fait plaisir 🙂

En attendant une éventuelle solution officielle pour les retrouver, vous pouvez passer par cette page : http://www.pcworld.fr/infos/auteur,matthieu-sarter.htm

C’est vrai que j’ai lu pas mal d’articles dans la presse informatique sur la fabrication de microprocesseurs, mais celui-ci sort du lot.

D’ailleurs il soulève une question : sur le schéma de la méthode de Czochralski, on voit que le lingot créé est parfaitement cylindrique, mais d’un diamètre largement inférieur à celui de la cuve. Comment ce lingot peut-il être si parfaitement cylindrique sans contrainte apparente ?

Je pense que ça vient tout simplement du processus de cristallisation.

Le cristal pousse autour de la graine dans toutes les directions, donc si le silicium liquide est suffisamment homogène au départ (en composition et en température), la croissance doit se faire à peu près à la même vitesse dans toutes les directions.

Et le fait de faire tourner le tout autour de l’axe doit également jouer un rôle, en homogénéisant encore un peu plus les vitesses de croissance.

EDIT : J’ai trouvé ça, avec des explications assez détaillées : http://rcswww.urz.tu-dresden.de/~cwinkler/poverview.htm

C’est donc le contrôle précis de la température et de la vitesse de levage qui permettent d’assurer la forme quasi parfaite, la rotation (qui apparemment s’applique aussi à la cuve) permettant d’améliorer le contrôle sur la température.

Et avec service après-vente en plus 😉

Merci !

Quelques détails tout de même:

– on dit pas « vernis » mais « résine »

-on dit pas « projecteur » mais « scanner » (même en français). Bon après ya peut-être une traduction mais personne ne l’utilise 😀

-Le scanner ASML montré est une machine EUV (extrem UV), pas encore en production. Une photo d’un ASML NXT est plus adaptée.

-Pour faire les transistors les étapes d’implantation sont essentielles, ce serait bien d’en parler 😀

-« Le masque ne comporte en général le schéma que pour un seul die » c’est faux, pour les CPU en tout cas, c’est généralement 4 voir 6 chez Intel / AMD. Un champ d’exposition fait 22*32 mm², donc ya la place de caser plusieurs CPU dedans. C’est pour faire des puces plus grosse que ça que ça devient sportif 😀

-« Le processus est ensuite répété une petite dizaine de fois » : sur du 22 / 14nm chez Intel on doit plus être à 30 exposition au total, sans compter le double patterning…

my 2 cents!

C’est toujours marrant de voir un processus de fabrication de plusieurs milliers d’étapes résumé en 3 paragraphes 😀

Quand tu parles d’implantation, c’est le différents processe de dopages substrat?

@toto408>

Un champ d’exposition fait 22*32 mm² => on parle de réticule non? moi je connais les pizzas, ou on met plusieurs puces sur un même wafer… en phase de test.

Sinon oui pour les multiples phases d’exposition

, quand on a 5 a 10 masques pour le Front End, et 12 métaux en Double patterning+vias, et la partie packaging qui se fait ensuite, on passe presque a 50 expositions (au doigt levé). Je n’ai pas tous les détails techniques, mais oui, c’est simplifié.

Ceci étant dit, c’est parmi les meilleurs articles de vulgarisation d’un process de chip.

Et L’auteur ne peut connaitre tous les détails d’une techno 14nm non encore stabilisée ni commercialisée.

Scanner, c’est le terme qui désigne l’ensemble de la machine il me semble, non ?

Et dans le scanner, il y a un projecteur. Après, je sais pas si ce projecteur est qualifié de projecteur quand les spécialistes en parlent, mais là l’avantage c’est que c’est un terme que tout le monde comprend sans avoir besoin d’expliquer ce que c’est 😉

Même remarque que barlav, c’est pas le dopage ça ?

C’est noté, mes connaissances n’étaient peut-être pas très à jour sur ce plan 🙂

Ma formulation n’était pas forcément très claire : ce qui est répété une petite dizaine de fois, c’est le processus de création d’une couche de piste, et je précise qu’entre chaque couche de piste, on a une couche d’interconnexion. Donc la dizaine de répétition fait une vingtaine d’exposition (c’est bien une exposition pour la couche d’interconnexion et une pour la couche de circuit, non ?). J’avais en tête 8-9 couches de circuits sur un processeur, d’où la petite dizaine.

😀

D’où le « principales étapes » en intro 😉

Comme dirait Fermat, j’avais fait un article véritablement merveilleux et plus complet sur le sujet mais ce site est trop étroit pour le contenir 🙂 (bon, j’avoue, j’aurais pas forcément su le faire de façon beaucoup plus détaillée…).

@barlav> Nan un masque ça fait 88mm x 128mm de surface active (la taille totale ce doit être en gros 20 x 20cm²;), et ya une réduction d’un facteur 4 par l’optique de projection. Un champ d’exposition sur le wafer fait 22*32 (maximum), donc ya la place pour caser des CPU (et un peu moins de GPU, qui sont souvent bien plus gros!)

Et oui l’implantation c’est le dopage, j’ai effectivement lu un peu trop vite et c’est cité 😀

Et je suis bien d’accord que c’est un très bon article de vulgarisation 🙂

@Matt> Scanner c’est que la projection, l’autre partie (qui dépose, cuit et développe la résine) s’appelle un « track », le tout étant appelé un « link » (link chez Intel en tout cas, à vérifier pour les autres). Je suis d’accord pour le fait que c’est bien plus compréhensible « projecteur » par contre, d’ailleurs je pense reprendre le terme quand j’aurai à expliquer ça à des gens normaux 😀

Pour l’interconnexion on est sur 11/12 niveau de métal sur les dernières technos, mais effectivement j’avais mal compris 🙂

En tout cas bravo pour l’article, c’est pas forcément facile d’avoir les infos quand on baigne pas dedans 🙂

@Matt> Avec les métaux en double patterning, il faut au moins le double d’étapes pour fabriquer juste une couche.

Je n’ai pas trouvé gd chose, mais GloFo et Intel l’utilisent de sur sur leurs dernières technos.

http://spie.org/x35993.xml

En gros on fabrique un masque intermédiaire qui va servir a faire les fronts montants et descendants autour de ce pattern, puis on vire ce motif et on ne garde que les fronts.

Sans aller dans les détails, ya plusieurs chose très différentes quand on parle de double parterning: ça peut être double exposition ou passer par des spacers (l’article Wikipédia est très bien fait à ce propos http://en.wikipedia.org/wiki/Multiple_patterning )

Y’avait un article sur le EUV et le 11nm sur semiwiki qui parlait de quintuple patterning pour le 11nm, et je pense donc qu’on doit être sur du quadruple patterning sur du 14nm… (en même temps 14 nm de demi pitch ça veut dire 30 nm de pitch, le pitch mini en 193nm immersion c’est en gros 75 nm, donc faut bien aller chercher le reste). Le gros bordel reste l’alignement de toutes les couches entre elles…

Une petite question : est ce qu’un processeur est sensible à un champ magnétique intense ? exemple : gros aimant ou champ magnétique artificiel ? Merci