Cette semaine dans La Question Technique, intéressons-nous à un élément qui évolue de moins en moins sur nos cartes mères et dont les processeurs cherchent de plus en plus à s’affranchir, en prenant à leur compte une partie de ses fonctions : le chipset.

Plus proche compagnon du processeur, le chipset est en quelque sorte le « routeur » interne de l’ordinateur, son rôle étant d’assurer la communication entre les différents éléments constituant l’ordinateur, mais aussi les périphériques externes, en gérant différents bus d’entrée/sortie.

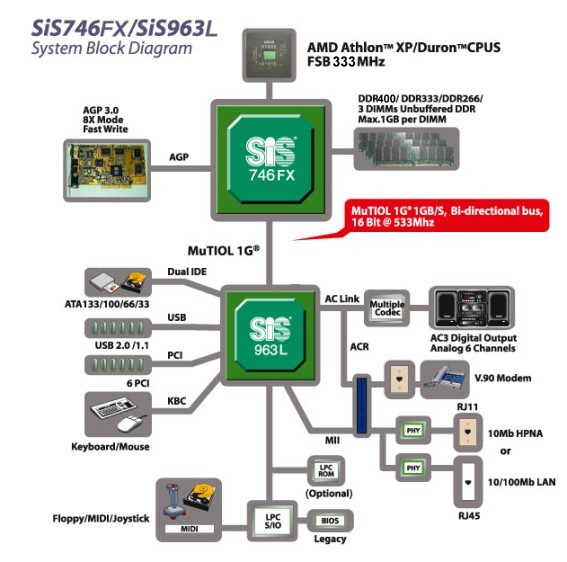

Comme son nom l’indique (« ensemble de puces » en anglais), le chipset était initialement constitué de plusieurs puces, le plus souvent deux : le Northbridge et le Southbridge.

Le Northbridge

Le Northbridge est la partie du chipset gérant les entrées/sorties les plus performantes :

- le bus processeur,

- le bus mémoire,

- les bus d’extension « rapides » (PCI, AGP, PCI-Express 16x)

Comme le Northbridge assure la communication avec le processeur, il doit donc être adapté à ce dernier, en gérant le bus processeur correspondant : révisions successives du FSB pour les puces Intel du 486 au Core 2 et AMD du 486 au K6-II, EV6 pour le K7 (Athlon) et HyperTransport pour les K8 (Athlon 64) et supérieurs, QPI pour les Core i sur socket 1366.

Quand le chipset intègre une puce graphique (IGP), c’est généralement au sein du Northbridge qu’elle est intégrée, pour qu’elle puisse accéder à la mémoire avec un maximum de vitesse.

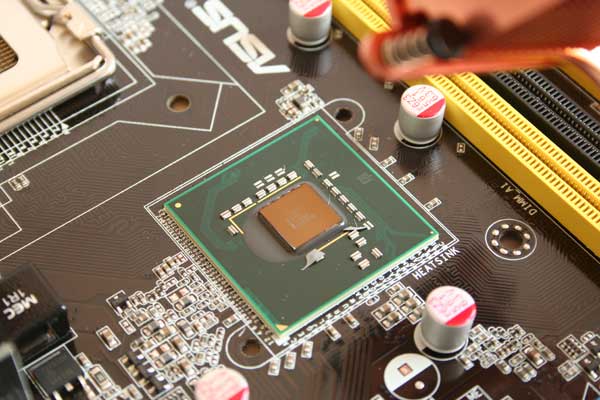

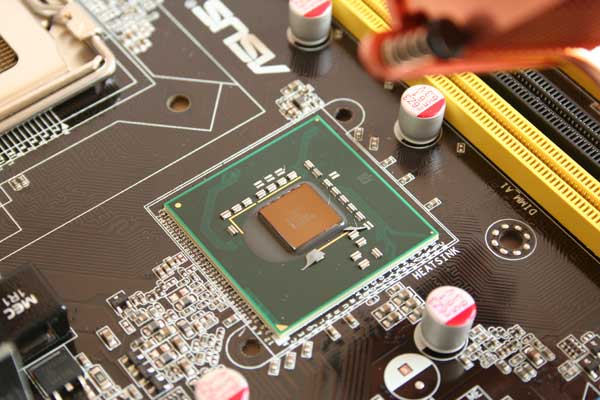

Du fait de son rôle, il est généralement situé dans la moitié haute des cartes mères, à proximité du socket CPU, des slots mémoire et du premier slot d’extension.

Le Southbridge

Le Southbridge a pour sa part la responsabilité des entrées/sorties « lentes » : PCI (depuis l’arrivée du PCI-Express), ATA, USB, ISA, Parallèle, série, PS/2, etc…

Il se place généralement sur la moitié inférieure de la carte mère, entre les slots d’extension et les ports ATA.

Aujourd’hui, on y trouve souvent aussi des lignes PCI-Express supplémentaires, qui viennent compléter celles gérées par le Northbridge (ou directement par le processeur), qui sont généralement dédiées à la carte graphique tandis que le Southbridge prend en charge les autres périphériques PCI-Express.

La connexion entre le Northbridge et le Southbridge se fait en général via une interface propriétaire, obligeant à utiliser deux puces issues d’un même constructeur, mais avec la possibilité de réaliser diverses combinaisons, pour moduler les caractéristiques de la machine.

Intel s’était particulièrement spécialisé dans la multiplication des références il y a quelques années, avec plusieurs dizaines de Northbridge compatibles avec les Core 2 et pouvant être couplés à plus de vingt Southbridge (les ICH) différents (du moins en théorie, car en pratique la plupart des combinaisons n’étaient pas supportées, même si l’interface était la même). Par exemple, les Northbridge P45 et G45 pour le Core 2 Duo pouvaient tous deux être couplés à deux Southbridge, les ICH10 et 10R, qui se différentiaient sur le support ou non du RAID, tandis que le G41, de même génération, était généralement proposé avec un ICH7 bien plus ancien, entrée de gamme oblige… Et il y avait encore pas moins de cinq autres Northbridge et deux autres Southbridge dans cette génération…

Une intégration toujours plus poussée

Avec la croissance des performances des machines, l’architecture système classique, avec le contrôleur mémoire dans le chipset, a fini par atteindre ses limites. Elle nécessitait en effet de câbler sur la carte mère à la fois un bus mémoire très rapide et un bus processeur très rapide, quasiment tout ce qui passe par le bus mémoire devant aussi passer par le bus processeur.

Ceci complexifiait la conception et la fabrication des cartes mères, alors qu’en dehors des accès mémoire il était possible de se contenter d’un bus bien moins rapide.

Pour maximiser les performances et simplifier les cartes mères, les constructeurs de processeurs ont donc commencé à intégrer le contrôleur mémoire dans le processeur. Outre le gain en complexité, cette intégration permet également de réduire les latences de la mémoire. Sur PC, c’est AMD qui a lancé ce principe avec ses Athlon 64, suivi quelques années plus tard par Intel sur les Core i.

Cette intégration a mené à une diminution de l’importance du Northbridge, qui est de plus en plus souvent fusionné avec le Southbridge.

Notons toutefois que l’intégration du contrôleur mémoire au processeur n’engendre pas nécessairement un chipset à mono-puce (le chipset X58 des premiers Core i7 était couplé à un Southbridge ICH10), mais aussi à l’inverse que l’intégration du contrôleur mémoire n’est pas indispensable à la réalisation d’un chipset à une seule puce. nVidia avait par exemple connu un certain succès sur les ordinateurs portables de petite diagonale avec son chipset 9400M avec IGP, qui facilitait grandement l’intégration dans une petite machine grâce à sa puce unique qui pouvait remplacer trois puces dans une configuration à chipset Intel (le Northbridge, le Southbridge et un GPU d’entrée de gamme, l’IGP du 9400M étant nettement plus performant que l’IGP Intel de l’époque).

Toujours dans une optique de gains de performances et de simplification de la carte mère, Intel a également choisi d’intégrer une partie du contrôleur PCI-Express au processeur, pour gérer les ports dédiés aux cartes les plus gourmandes (principalement les cartes graphiques), menant à des chipsets fortement simplifiés, ne comportant plus qu’un Southbridge, désormais connecté au processeur avec une interface « lente » (donc moins complexe à câbler sur la carte mère) : le DMI 2.0 qui relie les puces Core i en LGA 115x (Northbridge intégré) à leur Southbridge, ne supporte par exemple que 20 Gbit/s, contre plus de 100 Gbit/s pour l’interface QPI qui relie les Core i en LGA 1366 à leur Northbridge externe.

Un marché de plus en plus fermé

Historiquement, les fabricants de processeurs proposaient des licences sur leurs bus processeur, ce qui a permis à de nombreux constructeurs de se positionner sur ce marché (SiS, Via, C&T, nVidia, ATI, ALI…), parfois même à la place des constructeurs de processeurs, qui ne proposaient pas leurs propres chipsets. Intel n’a par exemple commencé à proposer ses propres chipsets qu’à partir du 486, avec les chipsets de la série 400, qui ont duré jusqu’au Pentium II, tandis qu’AMD n’a réellement commencé à produire des chipsets en volume que récemment (auparavant, AMD a produit quelques chipsets en petite série pour accompagner certains lancements ou pour ses processeurs de serveurs), après le rachat d’ATI.

Jusqu’aux K6, les processeurs AMD étaient souvent associés à des chipsets Intel, les deux fondeurs utilisant à l’époque le même bus processeur et le même socket, puis c’est Via qui a raflé le gros du marché des chipsets pour les premiers K7, avant qu’nVidia ne débarque avec succès sur le marché au début des années 2000, accompagnant avec brio les heures de gloires de l’Athlon XP, mais aussi et surtout de l’Athlon 64, suite à la collaboration entre AMD et nVidia pour la conception du bus HyperTransport. Profitant de l’intégration du contrôleur mémoire dans l’Athlon 64, le chipset nForce 3 a été l’un des tout premiers chipsets pour PC à se contenter d’une seule puce.

Mais l’intégration de fonctionnalités des chipsets dans les CPU est allée de pair avec une réduction drastique du nombre d’acteurs sur le marché des chipsets. D’abord, parce que du côté d’Intel, il n’y a tout simplement pas de licences sur les bus QPI et DMI, rendant impossible la réalisation de chipsets compatibles. Ensuite, parce que l’un des points clés pour le choix d’un chipset était justement les performances de son contrôleur mémoire. En excluant ce circuit du chipset, les possibilités de différenciation entre les constructeurs se sont réduites, tandis que la valeur des chipsets a diminué, rendant le marché bien moins intéressant.

En pratique, on ne trouve donc aujourd’hui quasiment plus que des chipsets AMD sur les cartes mères pour CPU AMD et Intel pour les cartes mères pour CPU Intel.

Vers la fin des chipsets ?

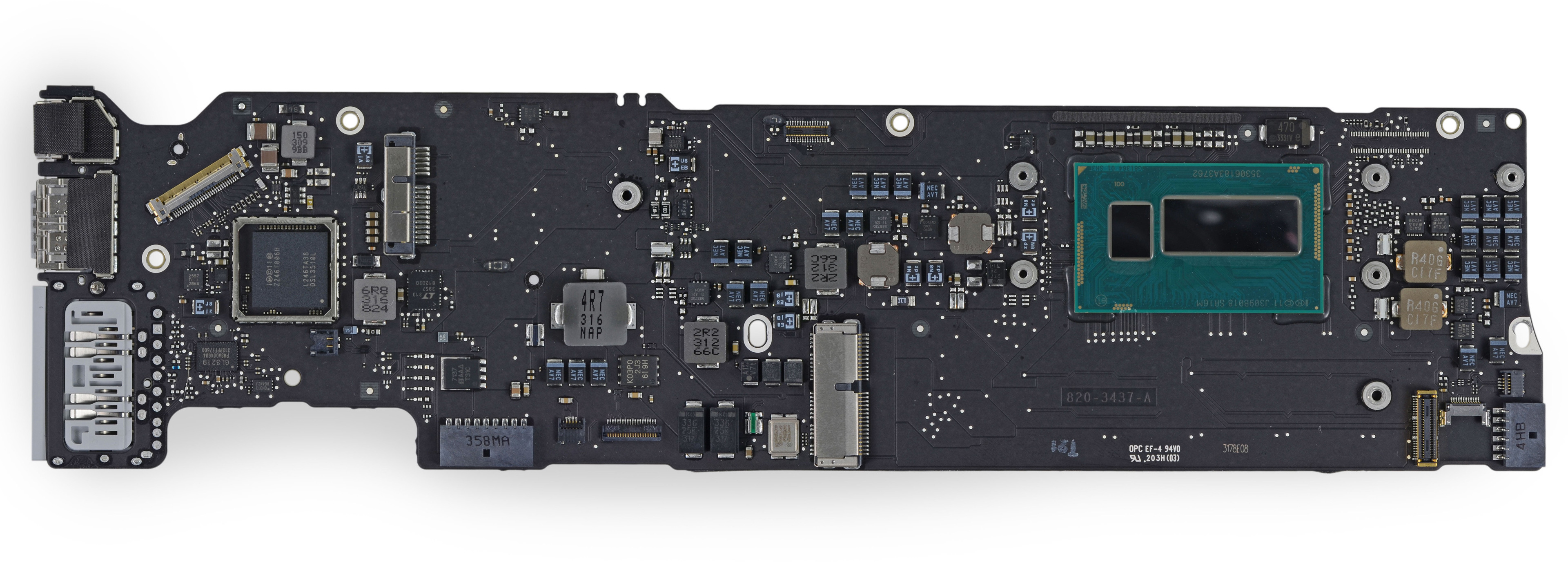

À force d’intégrer les fonctionnalités les plus importantes du chipset dans le CPU, il se pourrait bien que le chipset finisse par complètement disparaître, généralisant ainsi à tous les ordinateurs le principe du System on a Chip (SoC), qu’on trouve déjà dans le monde de l’embarqué, dans les smartphones et dans les tablettes.

L’architecture SoC fait bien sûr perdre en souplesse, puisqu’il est plus difficile de proposer un même processeur avec différents modèles de chipsets en fonction du segment visé, mais en contrepartie, elle permet d’économiser sur la conception de la carte mère, puisque la plupart des interconnexions rapides se retrouvent directement intégrées dans le processeur, sans avoir à être tracées sur le PCB de la carte mère. Elle peut également permettre de réduire un peu l’effet goulet d’étranglement que peut parfois induire le Southbridge : sa connexion avec le processeur est souvent bien plus lente que le cumule des interfaces qu’il propose. Le Z87 d’Intel propose par exemple plus de 110 Gbit/s de débit théorique sur l’ensemble de ses interfaces, mais ne communique avec le processeur que via un lien DMI 2.0 à 20 Gbit/s.

Cette intégration permet bien sûr également un gain de place, crucial pour la miniaturisation, et c’est sans doute pour ça que c’est par les puces mobiles ou pour nettop que sont arrivés les premiers SoC x86. Intel propose par exemple actuellement des SoC dans sa gamme Atom (SoC à un seul die), principalement pour tablettes, et dans sa gamme Core i ULV pour ultrabooks (le Southbridge reste sur un die séparé du CPU, mais intégré dans le même packaging). Du côté d’AMD, ce sont les APU Temash et Kabini qui ont inauguré l’intégration totale du chipset.

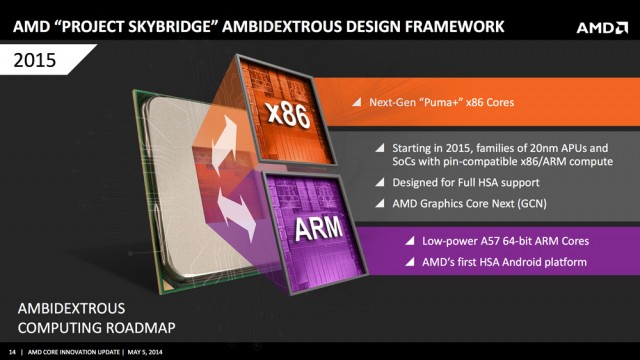

À défaut de permettre de la souplesse dans le choix des fonctionnalités, cette intégration de toutes les fonctions du chipset au sein du processeur pourrait par contre apporter une nouvelle forme de souplesse inédite : la possibilité de changer totalement d’architecture de processeur sans changer de carte mère…

En effet, si toutes les interfaces contrôlées par le chipset sont intégrées au processeur, celui-ci pourrait en arriver à ne plus communiquer avec la carte mère que via des interfaces standard (PCI-Express, USB…), totalement indépendantes de l’architecture du processeur.

AMD a d’ailleurs donné un premier aperçu de cette possibilité avec sa plateforme SkyBridge, qui permettra à une même base matérielle d’accueillir indifféremment des SoC ARM ou x86.

Le concept n’est toutefois pas encore poussé jusqu’au bout, puisqu’il reste des interfaces propriétaires, notamment pour la configuration du processeur, et surtout, parce que la partie logicielle de la carte mère doit forcément être adaptée à l’architecture du processeur. Il y aura donc probablement des cartes mères SkyBridge x86 et des cartes mères SkyBridge ARM, chacune compatible uniquement avec un type de processeur, même si elles sont physiquement strictement identiques.

Mais peut-être que dans quelques années une plus grande standardisation de ces éléments permettra d’apporter toute la souplesse que l’intégration du chipset peut théoriquement apporter, avec peut-être même un retour des cartes mères compatibles avec plusieurs constructeurs de processeurs… à condition que ces derniers le veuillent bien et se mettent d’accord pour standardiser les sockets…

Très bel article, merci !

ça nous fait toujours un coup de vieux lol ^^

Pour Skybridge, il faudrait regarder du côté de l’UEFI…

Si l’UEFI peut initialiser les périphériques, il peut aussi très bien identifier l’architecture CPU et basculer entre différents blocs de code.

Nope, faut aller plus bas niveau justement.

L’UEFI, c’est déjà du code qui est exécuté par le CPU.

Mais oui, c’est possible d’avoir un carte mère avec un double firmware et qui charge le bon en fonction du CPU détecté. Mais à priori, c’est pas ce qui est prévu avec Skybridge.

@Matt> Coreboot peu le faire, et après peu lancer tianocore pour le cpu qui vas bien (UEFI).

Merci pour l’info. T’aurais un peu plus de détails là dessus ?

Parce que j’ai du mal à comprendre comment ça peut marcher avec coreboot, qui ne remplace que le firmware de la carte mère.

La carte mère considère normalement que son firmware est du code compatible avec le CPU qui est monté dessus, et elle transmet ce code au CPU.

Pour qu’une même carte mère puisse gérer deux architectures de CPU différentes, il faudrait donc qu’elle intègre un système qui détecte le type de CPU pour lui passer le bon code. Coreboot peut être compilé pour ARM ou x86, et la carte mère doit passer le bon code au CPU.

Un simple remplacement du firmware par un firmware compatible avec deux types de CPU ne permettrait donc pas de gérer les deux types, il faut que au niveau matériel la carte mère embarque un système qui détecte le type de processeur et lui envoie le bon code.

L’appellation « chipset » (ensemble de puces) ne vient pas du fait que c’est constitué de plusieurs puces, northbridge et southbridge, mais justement du fait que ça regroupe plein de puces en une seule (ou deux) : contrôleur mémoire, horloge, contrôleur IRQ, contrôleur DMA, contrôleur ISA, contrôleur série, parallèle, clavier, disquette, etc. qui étaient historiquement toutes des puces séparées à l’époque du PC/XT.

La notion de chipset est apparue si je ne m’abuse avec le 286 ou 386, et c’est devenu vraiment connu du grand public avec le fameux chipset Triton sur le Pentium 75 avec le support de la RAM EDO.

Ah, le duel standard/spécifique !… En attendant le monde parfait, unifié, harmonieux (non, pas crédule à ce point !), toujours bien faite, la LQT, qui ne tue que si on ne la lit pas !

Comptent-ils faire plus de carte mère XL ATX pour avoir plus d’espace entre 3 ports pci express pour ventiler correctement 3 cartes graphiques double slot ?

Je pense qu’il serait bon de préciser que l’intégration croissante (unification des bridges, puis intégration au CPU) permet aussi de faire des économies d’énergie puisque les bus à haute vitesse deviennent beaucoup plus courts.

Ce n’est pas anodin pour les machines mobiles, même les laptops. À ce titre il est intéressant de noter que Carrizo aura un petit southbridge intégré (même s’il restera compatible avec un southbridge externe pour le desktop, afin d’avoir accès à plus de fonctionnalités).

[mode préhistorique]

putain mais alors c’est le southbridge de ma KT7 raid abit qui foutait la merde et qui m’empêchait d’avoir internet avec mon modem USB alcatel en mode raie manta verte!!!! France Telecom avait donc raison à l’époque?!

[/mode préhistorique]

😀

Moi j’avais une KG7 avec le même soutbridge VIA686B. Il suffisait de désactiver la gestion d’énergie USB pour que ça marche.

Bon, j’imagine que c’est 12 ans trop tard pour la solution 🙂

@arvernman> Le fait que ladite raie ait un fusible de 1.5A là où l’USB n’était pas supposé pouvoir fournir plus de 500mA devait jouer un peu… 😮

Non mais euh sté juste pour nous rappeler d’excellents moments que je parlais de ça, je suis vite passé au modem ethernet. C’est d’ailleurs grace à ce bug d’USB que j’ai mis un pied sur le forum rmgt (RIP).